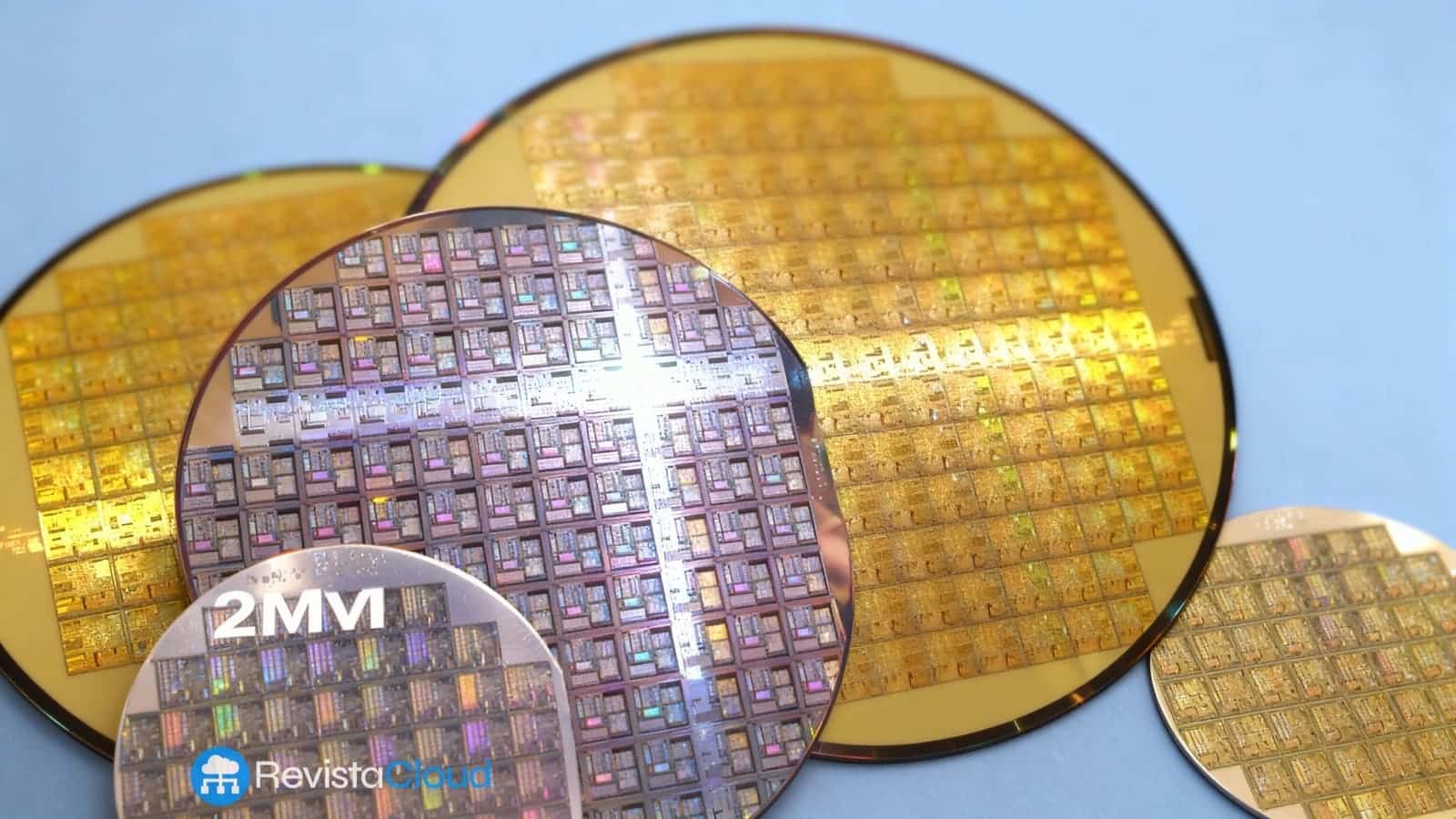

La industria del chip se enfrenta a una nueva contienda, una que no se definirá únicamente por las mejoras en benchmarks o por las novedades en GPU, sino más bien por la capacidad de producción. En el inminente salto a los 2 nanómetros, poseer la capacidad de fabricación se está transformando en un recurso estratégico crucial: aquellos capaces de asegurarse obleas con antelación tendrán la ventaja de lanzar aceleradores de Inteligencia Artificial (IA) más eficientes, mientras que los rezagados podrían quedar fuera del juego.

En el epicentro de esta competencia se encuentra TSMC, la fundición titánica que abastece a gran parte del mundo. El sector ha advertido durante meses que la demanda de nodos avanzados supera ampliamente la oferta. De hecho, el propio cuerpo directivo de TSMC ha admitido que su capacidad es insuficiente frente al enorme apetito de sus grandes clientes de computación avanzada.

El nodo de 2 nm supone un cambio de era, no es una simple mejora incremental. Incorpora una arquitectura innovadora de transistores tipo GAAFET/nanosheet, que optimiza simultáneamente el rendimiento, el consumo y la densidad. En un mundo donde el coste energético del cómputo pesa cada vez más en los presupuestos y en los límites físicos de los centros de datos, la eficiencia ha comenzado a tener un valor igual, o incluso mayor, que la potencia bruta.

El inicio de un nodo revolucionario normalmente lo dictan los calendarios de los principales fabricantes de móviles debido al volumen, la previsibilidad y los ciclos anuales. No obstante, el auge de la IA ha reconfigurado este panorama. Los grandes aceleradores y los ASIC para entrenamiento e inferencia están impulsando la demanda de capacidades avanzadas con una intensidad sin precedentes. Algunas publicaciones asiáticas han reportado un escenario de capacidad de 2 nm sumamente comprometida debido a las reservas de primer nivel, generando una creciente tensión entre el sector móvil y el de alto rendimiento.

Un nodo puntero no solo representa una mejora técnica; es también un cuello de botella comercial. En un mercado donde el retraso en el lanzamiento puede costar contratos millonarios, la prioridad es asegurarse un lugar en la línea de producción.

Añadiendo a la complejidad, incluso si se tuvieran suficientes obleas, persiste otro obstáculo: la transformación de esos fragmentos de silicio en sistemas colosales listos para IA. Los aceleradores actuales ya no son simplemente «un chip», sino conjuntos de chiplets, memorias y enlaces de alta velocidad en empaquetados cada vez más complejos. Las tecnologías de empaquetado avanzado, como CoWoS, se han convertido en un segundo cuello de botella. Estas dificultades no se resuelven de un día para otro, con análisis que proyectan la tensión en capacidad de empaquetado hasta el 2025 o 2026.

Este entorno tiene implicaciones concretas para los usuarios comunes. La limitada capacidad podría traducirse en costos más altos en hardware, servicios en la nube y eventualmente en productos. Además, la disponibilidad de nuevos lanzamientos dependerá de ventanas de fabricación más ajustadas, lo que podría provocar retrasos o limitaciones en la oferta. Por último, la eficiencia energética es un factor crucial, ya que los nodos más avanzados promueven un menor consumo por operación, algo vital para la economía real de la IA.

En el contexto geopolítico, un recurso industrial de tal magnitud acarrea ajustes en los planes de inversión, localización y acuerdos de suministro de las empresas y los países. En este escenario, Taiwán desempeña un rol central, y España, aunque de manera indirecta, percibe el impacto a través de costos, proyectos de centros de datos y acceso a tecnología en la economía digital. La carrera por los 2 nm es una pugna que define no solo el futuro de la tecnología, sino también la estructura económica y política global.