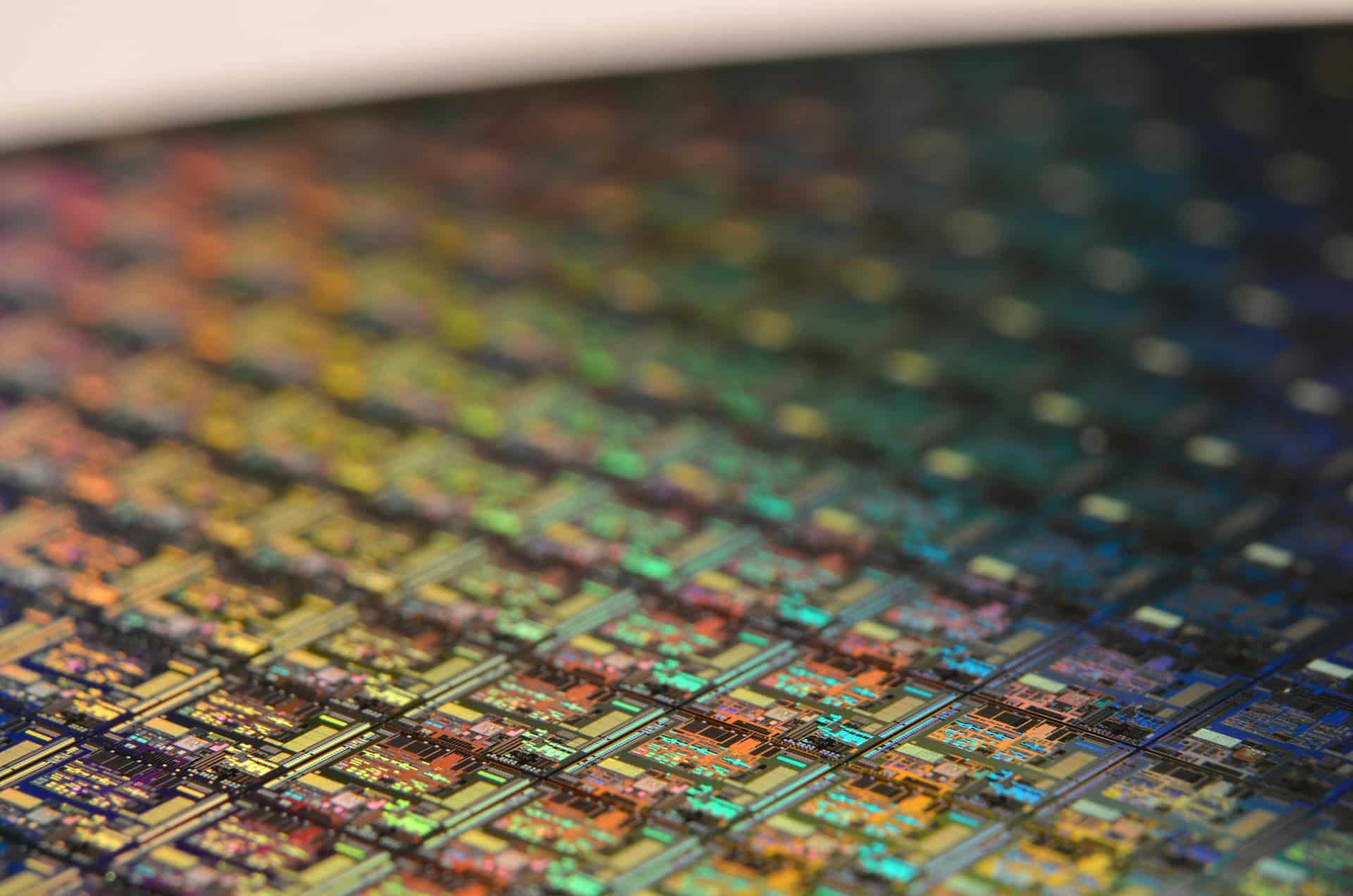

El mundo de los semiconductores, acostumbrado a transformaciones revolucionarias en su búsqueda por la miniaturización, se enfrenta ahora a un nuevo hito impulsado por la industria surcoreana. El Instituto Coreano de Ingenieros de Semiconductores ha publicado su ambicioso «Semiconductor Technology Roadmap 2026», planteando un panorama de innovación tecnológica que abarca los próximos 15 años y que visualiza el año 2040 como el inicio de una era con circuitos lógicos de «0,2 nm» y la implementación de innovadoras estructuras como CFET y la estructuración 3D monolítica.

Este visionario plan, compartido por ETNews, promete una significativa reducción del tamaño de los circuitos, una décima parte respecto a los estándares actuales, entrando en la escala del “ångström”, una medida para dimensiones menor que un nanómetro. Actualmente, la industria transita hacia arquitecturas de transistores más avanzadas; por ejemplo, Samsung ha lanzado su Exynos 2600, un chip móvil basado en un proceso GAA de 2 nm, fijando el estándar de vanguardia para 2025. Sin embargo, el desafío es aún mayor: alcanzar nodos lógicos de 0,2 nm para 2040, lo que implica adoptar tecnologías como CFET y la estructuración 3D monolítica para avanzar hacia la verticalidad y nuevas arquitecturas.

La cifra «0,2 nm» se presenta más como un símbolo de un avance tecnológico significativo que una medida física literal. En la práctica, sugiere una meta de escalado integrado por varios aspectos como densidad, eficiencia y nuevos materiales. La hoja de ruta es una declaración de intenciones de Corea del Sur para liderar en una fase donde los límites físicos de los actuales métodos de fabricación son cada vez más desafiantes.

La hoja de ruta considera nueve tecnologías esenciales para consolidar su liderazgo, entre ellas dispositivos y procesos de semiconductores, semiconductores para Inteligencia Artificial, interconexión óptica e incluso computación cuántica. Estas áreas resaltan que el futuro no solo dependerá del tamaño físico de los nodos, sino de la integración efectiva de todo el sistema tecnológico.

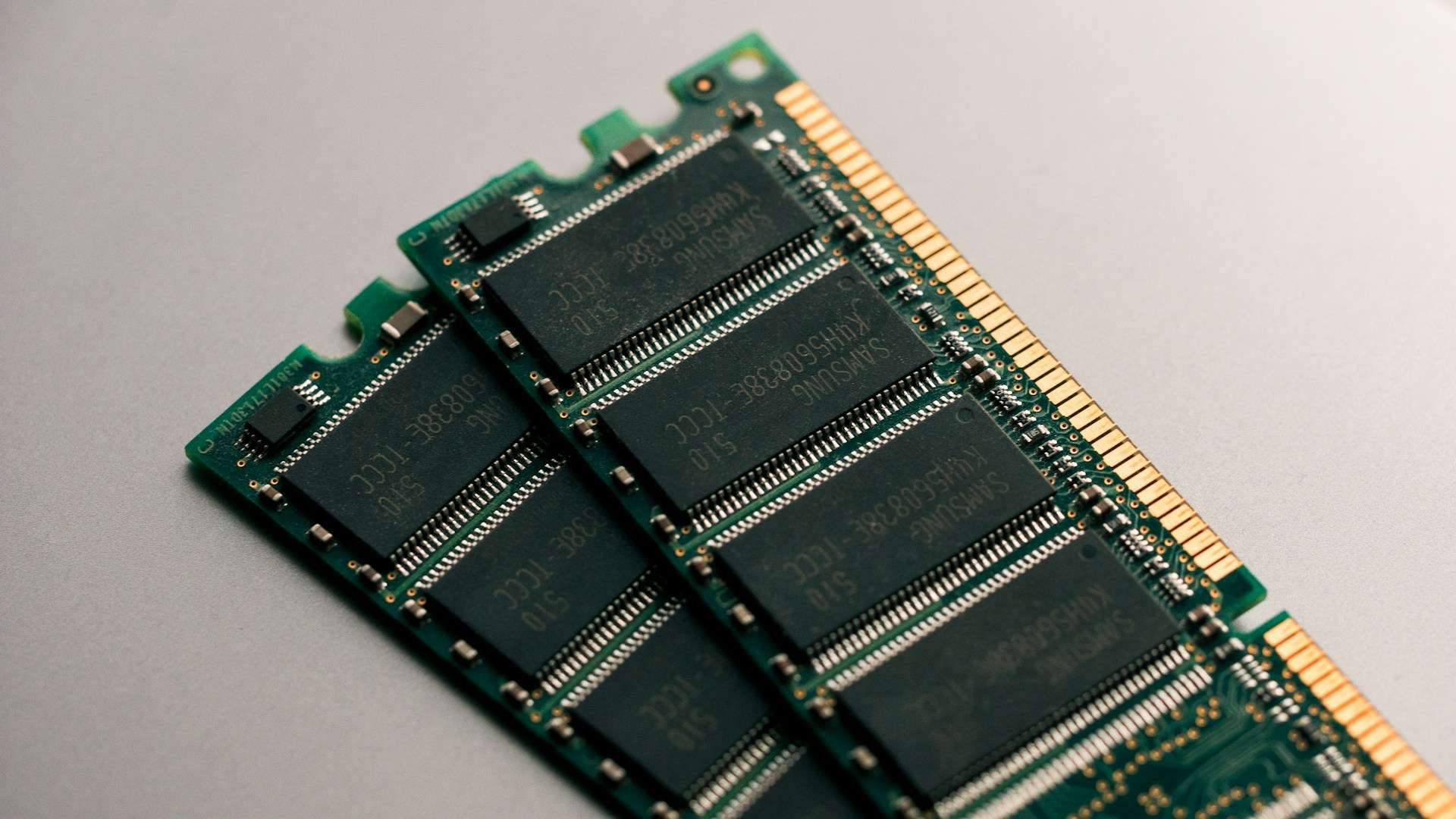

En el ámbito de la memoria, el informe es audaz, sugiriendo disminuciones en los circuitos de DRAM de 11 nm a 6 nm, así como un aumento en la capacidad de HBM de 12 capas a 30 o más. Esto refleja una dirección donde la capacidad de manejar y mover datos es tan crucial como la capacidad de cálculo bruta, especialmente en aplicaciones de alta demanda como la Inteligencia Artificial y sistemas de alto rendimiento.

Del mismo modo, el roadmap apunta al desarrollo de la NAND flash, aspirando a aumentar la cantidad de capas apiladas de 321 a un objetivo de 2.000. Este crecimiento vertical reitera la estrategia de la industria para abordar la complejidad creciente y las demandas de almacenamiento de los centros de datos y dispositivos globales.

Finalmente, dentro del campo de los semiconductores para Inteligencia Artificial, la proyección es clara: un salto de rendimiento medido en operaciones por segundo, esperando pasar de 10 TOPS por vatio a 1.000 TOPS para aprendizaje y 100 TOPS para inferencia en 15 años. Estas cifras no solo representan mejoras técnicas, sino también el deseo de Corea del Sur de estar en el centro de la próxima revolución tecnológica.

Este roadmap es mucho más que una mera predicción; es una hoja de ruta estratégica que guía la coordinación industrial, académica y administrativa, reafirmando la posición de Corea del Sur en el competitivo escenario global de la tecnología y los semiconductores. Así se consolida una visión donde la innovación y la cooperación son esenciales para enfrentar los desafíos del futuro tecnológico.