En el panorama de la tecnología de semiconductores, la litografía EUV de alta apertura numérica (High-NA) ha sido vista como un posible salvavidas ante los límites del escalado tradicional de chips. Sin embargo, las recientes conversaciones dentro de la industria están arrojando una visión menos optimista: la presencia de una máquina avanzada no garantiza una producción a gran escala sin un ecosistema maduro que la respalde. No es un problema de hardware aislado, sino del conjunto de herramientas y procesos que deben trabajar al unísono, siendo la corrección de proximidad óptica (OPC) un eslabón crucial.

La incertidumbre ha levantado cuestiones especialmente alrededor de Intel, que planea emplear High-NA EUV en su nodo 14A. Existe el temor de que los problemas con la OPC y la preparación del flujo de fabricación puedan retrasar sus ambiciosos planes. Para Intel, esta herramienta es clave en su estrategia para posicionarse nuevamente como líder en nodos avanzados. Sin embargo, las dificultades en la implementación de la OPC podrían complicar seriamente la producción en masa.

Por otro lado, TSMC, su principal competidor, parece adoptar una postura más cautelosa. A pesar de evaluar la tecnología High-NA, no muestra señales de adoptarla a corto plazo, argumentando que el costo y el retorno no son atractivos en el contexto actual. Esto refuerza su estrategia de exprimir al máximo la tecnología Low-NA existente antes de hacer la transición a High-NA. La decisión se basa en una ecuación pragmática de riesgo, coste y beneficio.

El desafío técnico es considerable. La High-NA EUV promete una mejor resolución y la posibilidad de reducir pasos de multipatronado, simplificando así la fabricación de chips complejos. Sin embargo, esto no es suficiente. La introducción de High-NA requiere una recalibración a fondo del escáner, los materiales, las máscaras, y sobre todo, un ajuste meticuloso en la OPC. Este paso es inevitablemente denso, ya que la OPC debe ajustarse a las nuevas condiciones ópticas y tolerancias, desafíos característicos de los nodos avanzados.

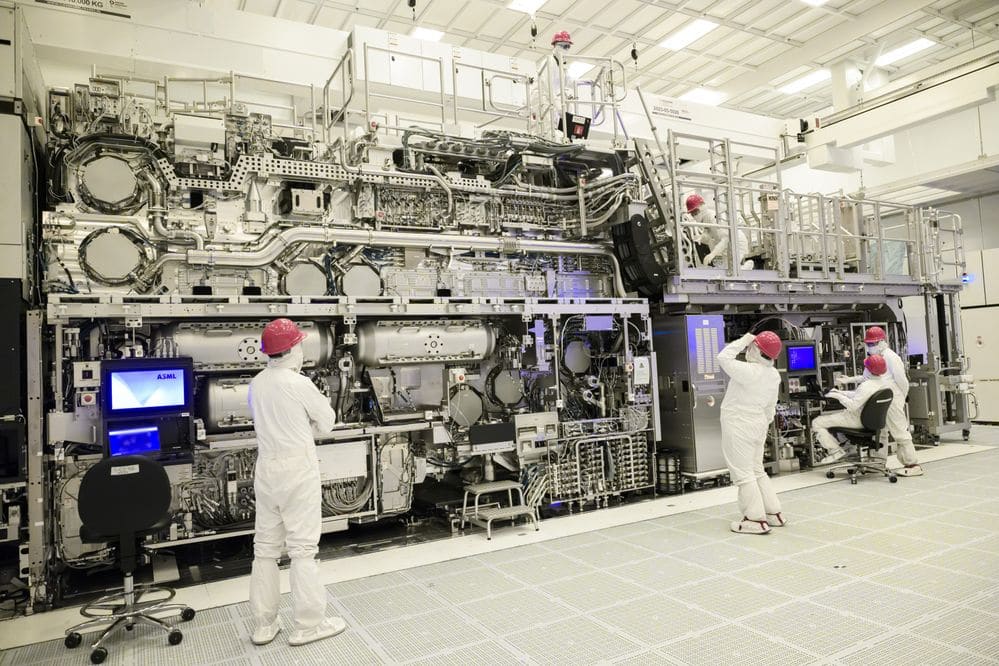

La reciente instalación de una herramienta High-NA (EXE:5200B) por parte de Intel marca un avance notable, moviéndose más allá del mero desarrollo de laboratorio. Pero este avance no se traduce automáticamente en capacidad productiva. Si el flujo de OPC y los controles asociados no alcanzan un nivel óptimo, el riesgo de que High-NA se convierta en un activo limitado o en una simple promesa a futuro es real.

El verdadero terreno de juego en esta competencia técnica y comercial es un delicado balance entre credibilidad, costes y atracción de clientes. Las herramientas High-NA representan inversiones colosales que solo se justifican si atraen un volumen de ventas significativo, y cualquier duda, especialmente sobre la madurez del flujo OPC, puede ser una barrera para la confianza de los clientes.

A través de estas posiciones, la industria reafirma una lección que nunca pierde vigencia: en semiconductores, la verdadera innovación se mide no solo por la existencia de tecnología avanzada, sino por su capacidad de ser integrada y explotada industrialmente. En el duelo entre Intel y TSMC, el escenario se presenta como un estudio de contrastes entre la ambición y el pragmatismo.